最近在学习AD24的过程中,发现一个问题:

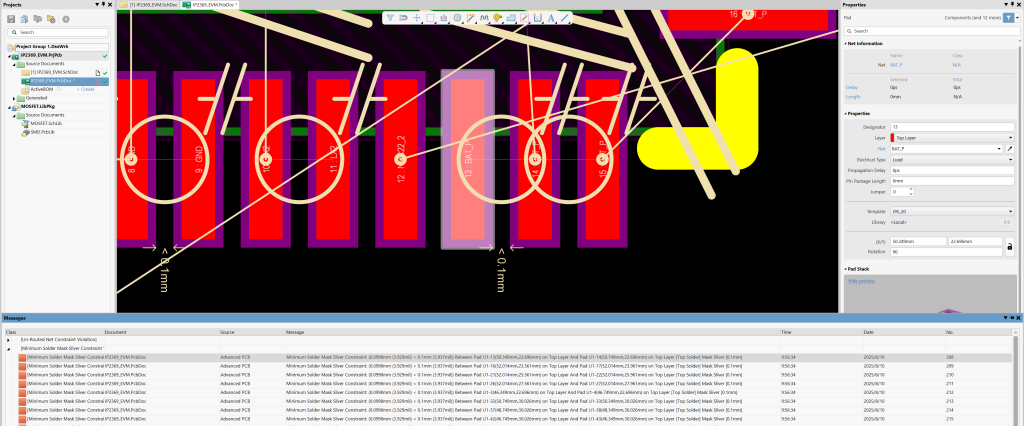

如截图所示,AD的DRC检查,报告了一个“[Minimum Solder Mask Sliver Constraint Violation] IP2369_EVM.PcbDoc Advanced PCB Minimum Solder Mask Sliver Constraint: (0.0998mm (3.929mil) < 0.1mm (3.937mil)) Between Pad U1-21(52.014mm,25.561mm) on Top Layer And Pad U1-22(52.014mm,25.961mm) on Top Layer [Top Solder] Mask Sliver [0.1mm]”的错误。

排查了一番,又手工计算了一下焊盘大小、阻焊扩展大小以及焊盘间距:

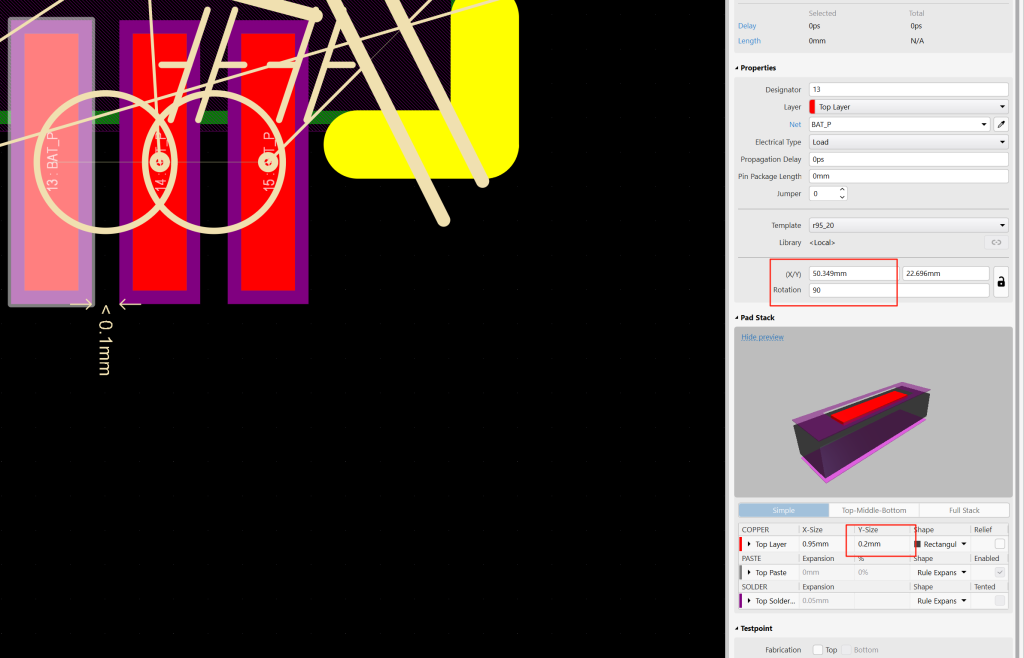

报错的临界两个引脚焊盘,左边的X是50.349mm,右边的X是50.749mm,焊盘中心距离0.4mm,焊盘宽度0.2mm,阻焊扩展跟随规则,设置的是0.05mm(SolderMaskExpansion),这些参数基本都是按照立创的工艺参数设置的,并且这个元件封装也是从立创EDA导入的,阻焊桥间距也是按立创的这篇文章:技术指导:阻焊基本设计,给的0.1mm的值。根据这些参数,手工计算0.4mm – 2 x 0.1mm – 2 x 0.05mm = 0.1mm,并没违反DRC设置的<0.1mm,可是AD提示的违规间距确是0.0998mm?

网上搜索一番后,发现有人提到了浮点数标准问题(链接找不到了,但现象是类似的现象),于是想到是不是浮点数精度问题,于是尝试把DRC rule里Minimum Solder Mask Sliver Constraint重新设置为0.099,再次DRC检查,发现不报错了,不知道这样有没有什么风险,先搞掉几个碍眼的报错再说。

博主友情提示:

如您在评论中需要提及如QQ号、电子邮件地址或其他隐私敏感信息,欢迎使用>>博主专用加密工具v3<<处理后发布,原文只有博主可以看到。